# 単一磁束量子回路を用いた単精度浮動小数点加算器の設計と測定

Design and Measurement of an Single-Precision Floating-Point Adder Using Single-Flux-Quantum Circuits

加藤 泰一, 彭 析竹, 山梨 裕希, 吉川 信行(横浜国大)

<u>Taiichi Kato</u>, Xizhu Peng, Yuki Yamanashi, Nobuyuki Yoshikawa (YNU)

E-mail: kato-taiichi-mw@ynu.ac.jp

## 1. はじめに

我々は、SFQ 回路を用いた将来のハイパフォーマンスコンピュータシステムのための基盤技術として再構成可能なデータパス(LSRDP: large-scale reconfigurable data-path)を提案している[1]。そのコンポーネント回路として半精度の浮動小数点加算器(FPA: floating-point adder)を  $2.5~\mathrm{kA/cm^2}$  Nb プロセスを用いて設計、試作し、 $20~\mathrm{GHz}$  での高速動作を実証している [2]。また、新しい SFQ 回路の作製プロセスである AIST  $10~\mathrm{kA/cm^2}$  Nb プロセスも開発されており[3]、臨界電流密度が大きくなったことでその高速性は  $2~\mathrm{GUL}$  に向上している。本研究では、AIST  $10~\mathrm{kA/cm^2}$  Nb プロセス用セルライブラリ[4]を用いて単精度浮動小数点加算器を設計し、動作評価を行った。

## 2. SFQ 浮動小数点加算器の構成

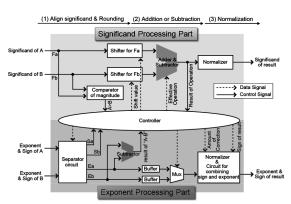

図1にSFQ浮動小数点加算器の構成図を示す。SFQ浮動小数点加算器は上部の仮数部演算部と下部の指数部演算部から構成される。主なコンポーネント回路として、仮数のシフト演算を行うシフター回路、シフトされた仮数の加減算を行う加減算器、正規化を行う正規化回路、全体の制御を行う制御回路がある。また、SFQ浮動小数点加算器の演算は3つのパイプラインステージで実行される。

# 3. SFQ 単精度浮動小数点加算器の測定

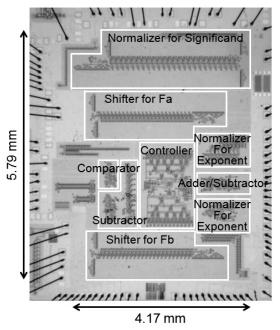

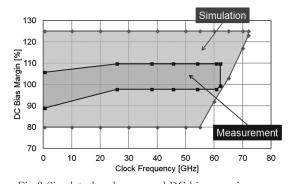

図 2 に単精度 FPA のチップ写真を示す。高速測定用入出力回路を除き、回路面積は 24.14 mm²、総接合数は 16130、消費電力は4.76 mWとなった。Verilogシミュレーションにおいて、最高動作周波数は72 GHz、目標動作周波数50 GHz におけるバイアスマージンは80~125%となった。

本回路の測定を行った結果、シフター回路からの途中出力の正常動作を確認した。図3に周波数に対する動作マージンのグラフを示す。測定結果における最高動作周波数は62.2 GHz、50 GHzにおけるバイアスマージンは97.7~109.7%となった。また、仮数部演算部については一部入力パターンで正常動作を確認した。詳細については講演にて述べる。

\*本研究に使用された回路は、(独)産業技術総合研究所 (AIST)の超伝導クリーンルーム(CRAVITY)において、AIST-ADP2プロセスを用いて作製された。AIST-ADP2は、(公財)国際超電導産業技術研究センター(ISTEC)のニオブ集積回路プロセスをAISTにて発展させたものである。

- N. Takagi, et al.: IEICE Trans. Electron., Vol. E91-C, No.3, pp. 350-355, 2008.

- 2. H. Park, et al.: IEEE Trans. Appl. Supercond., vol.19, no.3, pp.634-639, 2009.

- 3. S. Nagasawa, et al.: Physica C, vol.412-414, pp.1429-1436, 2004.

- Y. Yamanashi, et al.: IEICE Trans. Electron., vol. E93-C, no. 4, pp. 440-444, 2010.

Fig.1 Block diagram of the SFQ FPA

Fig.2 Chip photograph of SFQ single-precision FPA

Fig.3 Simulated and measured DC bias margins as a function of the clock frequency. The DC bias margins are normalized with the designed bias voltage ( $2.5~\mathrm{mV}$ ).

# 単一磁束量子回路を用いた飛行時間型質量分析用時間測定回路の冷凍機内に おける動作実証

Demonstration of a Single-Flux-Quantum Time-to-Digital Converter for Time-of-Flight Mass Spectrometry in a Cryo-cooler

佐野 京佑, 村松 祐希, 下田 知毅, 山梨 裕希, 吉川 信行(横浜国大);全 伸幸, 大久保 雅隆(産総研) SANO Kyosuke, MURAMATSU Yuki, SHIMODA Tomoki, YAMANASHI Yuki, YOSHIKAWA Nobuyuki (YNU); ZEN Nobuyuki, OHKUBO Masataka (AIST)

E-mail: sano-kyosuke-cw@ynu.ac.jp

#### 1. はじめに

現在,飛行時間型質量分析法(TOF-MS, Time of Flight Mass Spectrometry)は医療分野や化学分野を含む広い分野 で用いられている。近年,生体高分子の高精度質量分析に 向け超伝導ストリップイオン検出器(SSID, Superconducting Strip Ion Detector)の研究がされている[1-3]。SSID を用いるこ とで従来の検出器と比べ高い分子量分解能と高カウントレー トを実現する。しかし、SSID の実質的な応答速度は室温の増 幅器や増幅器までの配線長により制限されてしまう。

本問題を解決するため、我々は単一磁束量子(SFQ, Single Flux Quantum)回路[4]を用いた高分解能時間測定回 路(TDC, Time-to-Digital Converter)の開発をしている。SFQ 回路もまた超伝導技術を用いた回路であり SSID と同一の極 低温環境にて最低限の配線長での高速演算が可能となる。

今回, 時間分解能 100 ps, ダイナミックレンジ 1.6 ms の SFQ TDC 単体の冷凍機内における動作試験を行ったためそ の結果について報告する。

## 2. SFQ 時間測定回路の構成と動作

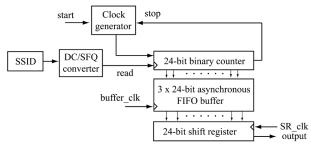

今回, AIST 2.5 kA/cm<sup>2</sup> 標準プロセス 2 を用いて製作され た24-bit SFQ TDC の冷凍機内動作試験を行った。SSID から 得られる検出信号の立ち上がりが数百 ps であるため TDC の 時間分解能は100 ps に,検出目標の最大分子量が60万Da であるためダイナミックレンジは 1.6 ms に設定した。SFQ TDC のブロック図を図 1 に示す。

本回路は 10 GHz で駆動する Clock generator (CG), 24-bit binary counter, 3 段の 24-bit First-In First-Out (FIFO) buffer, 並びに読み出し用 24-bit shift register(SR)から 構成される。start 信号をトリガーとして CG が駆動し, CG から 100 ps 間隔で出力される SFQ パルス数を counter にて計測 する。SSIDから得られる検出信号はDC/SFQ converter により SFQ パルスへと変換される。イオン検出時の read 信号により その時点でのカウントデータが FIFO buffer へと送られる。そ の後,1発のbuffer\_clk 信号とそれに続く24発のSR\_clk 信号 を 1 サイクルとした室温からの低速の入力により FIFO buffer に格納されたカウントデータを読み出し用 SR へと移し室温へ と読み出す。

Fig.1 Block diagram of the SFQ TDC

# 3. SFQ 時間測定回路の冷凍機内動作試験

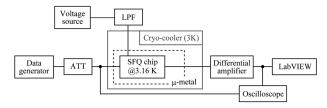

図2に示すように測定装置を構成し実験を行った。 室温のパルスパターンジェネレータから start 信号並びに

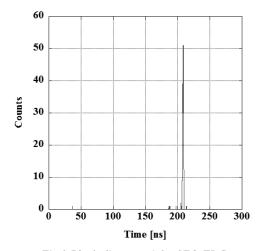

read 信号を SFQ TDC に直接入力し, start-read 信号間の時 間間隔の測定を1000回ずつ行った。図3に出力結果のヒスト グラムの一例(start-read の入力時間差は 200 ns)を示す。図 2 にて入力時間差に対応したピークが得られており、冷凍機 内での TDC の動作を確認した。

Fig.2 Measurement setup

Fig.3 Block diagram of the SFQ TDC

#### 謝辞

本研究に使用された回路は、(独)産業技術総合研究所 (AIST)の超伝導クリーンルーム(CRAVITY)において, AIST-STP2 プロセスを用いて作製された。

- 1. K. Suzuki, et al.: Rapid Commun. Mass Spectrom., Vol. 24 (2010) p.3290

- 2. A. Casaburi, et al.: Appl. Phys. Lett., Vol. 98 (2011) 172508

- 3. N. Zen, et al.: Physics Procedia, Vol. 27 (2012) p.356

- 4. K. K. Likharev and V. K. Semenov, IEEE Trans. Appl. Supercond., Vol. 1 (1991) p.3

# 磁気シールド構造を用いた断熱型磁束量子パラメトロンによる 8-bit Carry Look-Ahead Adder の設計と測定結果

Design and Measurement Results of 8-bit Carry Look-Ahead Adder Using an Adiabatic Quantum-Flux-Parametron

<u>井上</u>健太,竹内 尚輝, 山梨 裕希,吉川 信行 (横浜国大)

<u>INOUE Kenta</u>, TAKEUCHI Naoki, YAMANASHI Yuki, YOSHIKAWA Nobuyuki (YNU)

E-mail: inoue-kenta-gr@ynu.ac.jp

#### 1. はじめに

断熱型磁束量子パラメトロン(Adiabatic Quantum Flux Parametron; AQFP)回路 [1] は高速性と低消費電力性を特徴とする超伝導集積回路の1つである。AQFP 回路を用いていくつかの回路を設計したが、本来想定しなかったインダクタンス同士の磁気結合により回路の誤動作を引き起こしていることが判明した。そのため誤動作の原因となる磁気結合を小さくするために磁気シールド構造を提案した。その磁気シールド構造を用いて8-bit Carry Look-ahead Adder を再設計した。講演では設計した回路とその測定結果について発表する。

#### 2. AQFP Buffer

AQFP 回路では入出力インダクタンス  $L_{\rm in}$ と  $L_{\rm out}$ との間の磁気結合によりデータの伝搬を実現している[1]。しかし、その際に Exciting Line インダクタンス  $L_{\rm x}$ と  $L_{\rm in}$ 、 $L_{\rm out}$ との磁気結合  $k_{\rm xin}$ 、 $k_{\rm xout}$  が回路の動作に悪影響を及ぼしていることが判明した。 AQFP 回路の入出力電流は数マイクロアンペアから数十マイクロアンペアであり、Exciting Line を流れる電流は数ミリアンペアである。そのため、僅かな磁気結合であったとしてもその影響は大きくなってしまうので、回路正常動作化のためにはこれらの磁気結合  $k_{\rm xin}$ 、 $k_{\rm xout}$ を小さくしなければならない。

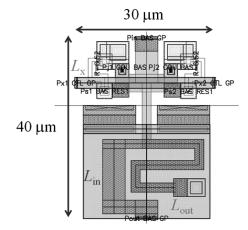

そこで、 $L_{\rm in}$ と  $L_{\rm out}$ を最上部にある配線層で覆う磁気シールド構造を検討した。そのレイアウトを Fig. 1 に示す。図の様に磁気シールド構造を採用したところ、 $k_{\rm xout}$  は 0.0031 から 0.0001 に、 $k_{\rm xin}$  は 0.0093 から 0.0001 にそれぞれ減少し、無視できる値となった。また、このシールド構造を用いた Buffer を連結した回路を低速下にて測定したところ、正常動作が得られた。

# 3. 8-bit Kogge-Stone Adder

Buffer だけでなく、NOT ゲートや、Majority ゲート、Splitter ゲートなどの基本的な論理ゲートも上述の磁気シールド構造を用いることで正常に動作するようになった。

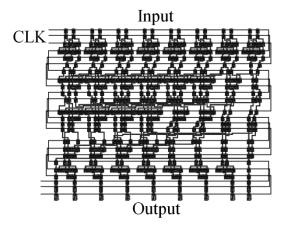

そこで AQFP 回路の実現性を示すために、最も基本的な計算を行い、かつ高速性を要求される加算器を設計した。最も単純な加算器の構成として ripple carry adder が挙げられるが、これは各ビット毎でキャリーの計算を行う必要があり、ビット数の増加に伴って計算時間が線形に増加してしまう。そのため、キャリーを並列に計算することで高速な演算を可能にした Carry Look-ahead Adder (CLA) [2] を採用した。CLA の種類として Kogge-Stone Adder 型、Brent-Kung型、Ladner-Fischer型など様々なタイプが存在しているが、今回はその中でも演算ゲートのファンアウト数が少ないKogge-Stone型の Full Adderを磁気シールドを用いた AQFP回路により設計した。

設計した AQFP Kogge-Stone Adder のレイアウトを Fig. 2 に示す。この回路の面積は 2.06×1.57 mm2 であり、Josephson 接合数は 1240 となっている。講演ではこの 8-bit Adder の測定結果について報告する。

Fig. 1 Layout of an AQFP Buffer

Fig. 2 Layout of an AQFP Kogge-stone Adder

## 謝辞

本研究に使用された回路は、(独)産業技術総合研究所 (AIST)の超伝導クリーンルーム(CRAVITY)において、AIST-STP2プロセスを用いて作製された。AIST-STP2は、(公財)国際超電導産業技術研究センター(ISTEC)のニオブ集積回路プロセスをAISTにて発展させたものである。

- N. Takeuchi, et al,. Supercond. Sci. Tech., vol. 26, (2013), p. 035010

- Jan M. Rabaey, et al., "Digital Integrated Circuits-A Design Perspective Second Edition," Peason Education International, (2003), pp.578-585

# 小型ジョセフソン電圧標準用極低温冷却システムの開発

Development of a Compact Cooling System for Josephson Voltage Standard

<u>佐々木 仁</u>, 山森 弘毅, 神代 暁(産総研); 小谷野 信一(株式会社サンジェム)

<u>SASAKI Hitoshi</u>, YAMAMORI Hirotake, KOHJIRO Satoshi (NeRI/AIST)

KOYANO Shinichi (SunJEM Co. Ltd.)

E-mail: hitoshi-sasaki@aist.go.jp

#### 1. はじめに

産業技術総合研究所では、株式会社サンジェムとの共同研究により、小型冷凍機を用いたコンパクトなジョセフソン電圧標準システムの開発を行っている。本システムにおいては、He ガスコンプレッサー以外の全ての要素部品を、標準規格の計測器の筐体(幅 450mm 高さ 270mm 奥行き 500mm 程度)に収納し、19 インチの計測ラックに搭載可能とすることを目標とした。ジョセフソン電圧標準は原理的に定期校正を必要としないため、産業界において超高安定な二次電圧標準器としての利用が期待される。ジョセフソン素子の極低温への冷却には、GM(Gifford-McMahon)型の、小型極低温冷凍機を使用した。ここでは冷却システムの構成、特長、および冷凍能力の制約等によって生じる問題点等について報告する。

#### 2. ジョセフソン電圧標準素子

本装置の中核となるジョセフソン電圧標準素子(以下「チップ」と略す)には、産総研の独自技術である NbN/TiN/NbN 型のジョセフソン接合が約 65,000 個集積されている[1]。このチップは、最大出力 2V のバイナリ型 D/A 変換回路の機能を有し、分解能は 10bit(1mV)である。また入力するマイクロ波周波数 fを変える事により、任意の電圧 V= $Nf/K_{J-90}$  を出力できる。ここで、N は接合数、 $K_{J-90}$  = 483 597.9 GHz/V はジョセフソン定数である。10V 発生用のチップは発熱が 100mW 程度と比較的大きく、またマイクロ波同軸ケーブルやバイアス配線等の信号ケーブルによる外部からの熱流入も 300mW 程度になる。二次標準器としての利用には、10V 以上の出力電圧が必須であるが、室温の精密電圧増倍回路[2]を補用してチップの出力電圧を 2 V に抑えることで、極低温部の熱負荷が抑制され、小型冷凍機の採用が可能となった。

#### 3. チップキャリア

チップキャリア全体の外観を Fig.1 に示す。銅製のチップ キャリア筐体とチップ間の冷却はチップ裏面に取り付けた 0.5mm 厚のサファイア基板を介して熱伝導により行う。チップ キャリア用プリント基板には、入手の容易な、汎用の 4 層 0.6mm 厚の薄型 G10 グラスファイバー基板を使用した。磁性の影響を避けるため、銅箔パッド部の保護膜には非磁性の金フラッシュメッキを選択した。またチップとプリント基板との電気的な接続には、ヒートサイクルに強い Al 線のワイヤー・ボンディングおよびリボン・ボンディングを併用した。

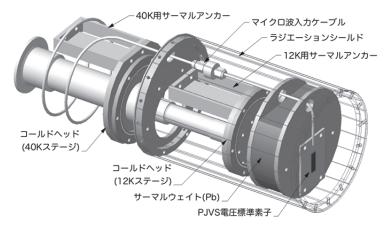

#### 4. クライオスタット

チップは CTI 社 Model22 型極低温冷凍機のセカンドステージにマウントされ、伝導冷却によって 12K に冷却される。クライオスタットの構造図を Fig.2 に示す。全ての GM 型冷凍機と同様に、Model22 型極低温冷凍機も冷凍サイクルに同期した 100mK を超える熱振動が発生する。通常は、チップキャリアとコールドヘッド間に円盤状のステンレスのシムを挿入し、熱抵抗を大きくすることにより温度変動を減少させるが、今回使用する小型の極低温冷凍機は冷凍能力に余裕がないため、熱抵抗を大きくして温度変動を抑える代わりに、10K においても他の物質と比較して例外的に大きな比熱を有する鉛のブロックをコールドヘッドに付加して、温度変動を軽減する方法を試みた。この結果、冷凍能力を損なわずに、チップの温度変動を 10mK 以下に抑制できることが確認できた。

一方、標準規格の計測器への収納のために、極低温冷凍機を横置きに設置する必要があるが、セカンドステージ先端に設置された約500gの鉛ブロックにより二段目のディスプレーサ部分へのたわみ加重が発生する。そこで、サーマルウェイトをセカンドステージと熱的にカップルさせて、かつ機械的には切り離すために、長さ約30mmの銅網線を12本並列に使用したフレキシブルな「サーマルリンク」を熱伝達に用いた。この方法により、ディスプレーサ部分にたわみ加重を発生させることなく、1W/K以下の良好な熱伝導が得られている。

- H. Yamamori, T. Yamada, H. Sasaki, S. Kohjiro, IEICE Trans. Electron., Vol. E95-C, No.3, March (2012)

- 2. H. Sasaki, H. Yamamori, T. Yamada, A. Shoji, S. Kohjiro, CPEM Digest, 2010, Deajon, Korea

Fig.1. PJVS-Chip and Chip-Carrier.

Fig. 2. Schematic view of Cryostat.

# バイクリスタル基板を用いた $BaHfO_3$ 添加 $SmBa_2Cu_3O_y$ 薄膜の 粒界電流特性に関する検討

Investigation of current characteristics at grain boundaries on the BaHfO<sub>3</sub>-doped SmBa<sub>2</sub>Cu<sub>3</sub>O<sub>V</sub> films using bicrystal substrates

<u>鶴田 彰宏</u>, 吉田 隆, 一野 祐亮(名大); 一瀬 中(電中研); 松本 要(九工大); 淡路 智(東北大) TSURUTA Akihiro, YOSHIDA Yutaka, ICHINO Yusuke (Nagoya Univ.);

ICHINOSE Ataru (CRIEPI); MATSUMOTO Kaname (Kyushu Inst. Tech.); AWAJI Satoshi (Tohoku Univ.) E-mail: tsuruta-akihiro11@ees.nagoya-u.ac.jp

## 1. はじめに

BaHfO<sub>3</sub>(BHO)は、PLD 法や CVD 法などの気相成長で作製した REBa<sub>2</sub>Cu<sub>3</sub>O<sub>y</sub>(REBCO)薄膜内で REBCO の c 軸方向に伸びたナノロッドを形成し、ナノロッドに平行な磁場に対して強いピンニング力を有することが知られている。我々の研究においても、PLD 法を用いて LaAlO<sub>3</sub> 単結晶基板上に BHO 添加 SmBa<sub>2</sub>Cu<sub>3</sub>O<sub>y</sub>(SmBCO)薄膜を作製し、その磁場中超伝導特性及び微細構造を検討してきた[1]。興味深いことに、無添加 SmBCO 薄膜の 77 K 自己磁場における  $J_c(J_c^{self})$ が、同じ条件で作製した場合においても、1.5~4.0 MA/cm² の間でばらつきが生じるのに対し、BHO 添加 SmBCO 薄膜では、4.0 MA/cm² を超える薄膜が再現性良く作製可能であることが経験的にわかっている。この原因のひとつとして、BHO 添加 SmBCO 薄膜において粒界電流特性が向上している可能性が考えられる。

そこで本研究では、BHO ナノロッドの導入が SmBCO 薄膜の粒界電流特性に与える影響を明らかにすることを目的として、LSAT バイクリスタル基板上に BHO 添加 SmBCO 薄膜を作製し、その超伝導特性を検討した。

# 2. 実験方法

BHO 添加 SmBCO 薄膜及び無添加 SmBCO 薄膜は PLD 法を用いて、[001]チルト粒界(5°)の LSAT バイクリスタル基板上に作製した。BHO の添加方法にはターゲット交換法を用いた。作製した薄膜の結晶性、配向性を X 線回析法(XRD)、超伝導特性を直流四端子法で測定した。

# 3. 実験結果及び考察

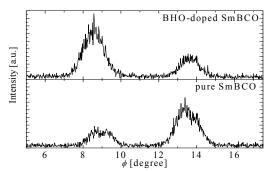

Fig. 1 にバイクリスタル基板上に作製した、無添加 SmBCO 薄膜及び BHO 添加 SmBCO 薄膜における(102)面の φ スキャン測定結果を示す。2 つの薄膜において、10°近傍に 5°間隔で 2 つのピークが観察された。このことから、無添加 SmBCO 薄膜及び BHO 添加 SmBCO 薄膜のどちらにおいても、SmBCO 母相が人工粒界を挟んで 5°回転して成長しており、BHO 添加が粒界傾角に影響していないことがわかった。

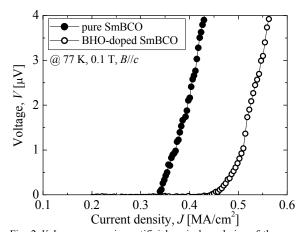

粒界を挟んだ無添加 SmBCO 薄膜及び BHO 添加 SmBCO 薄膜の  $T_c$  はそれぞれ 92.7 K 及び 91.1 K であり、粒界を挟んでいない場合の 92.5 K 及び 90.7 K と同程度であった。また、 $J_c$  self は、それぞれ 0.96 MA/cm² 及び 1.03 MA/cm² であり同程度であった。しかしながら、粒界を挟んでいない無添加 SmBCO 薄膜(2.63 MA/cm²)及び BHO 添加 SmBCO 薄膜(1.62 MA/cm²)の  $J_c$  self と比較すると、その低下率はそれぞれ 63%と 36%であり、人工粒界における  $J_c$  低下の影響がBHO 添加 SmBCO 薄膜において減少していると考えられる。Fig. 2 に 77 K、0.1 T における粒界を挟んだ無添加 SmBCO

薄膜及び BHO 添加 SmBCO 薄膜の V-J 曲線を示す。 どちらの場合においても、人工粒界を挟んだ場合に特有の  $V \approx I^n$  に従わない線形な V-J 特性が観察された[2]。 ただし、BHO 添加 SmBCO 薄膜においては  $1 \mu V$  以下の領域で曲線がカーブしているような挙動が見られる。 この挙動に関する明確な原因は不明であるが、粒界傾角や粒界特性の異なる基板の比較から、粒界の影響が減少するにしたがって、V-J 特性が  $V \approx I^n$  に近づく傾向が見られていることから[3]、BHO 添加によって SmBCO 薄膜の粒界特性が向上している可能性も考えられる。

Fig. 1  $\phi$ -scan measurements of the pure and BHO-doped SmBCO films deposited on bicrystal LSAT substrates.

Fig. 2  $\emph{V-J}$  curves crossing artificial grain boundaries of the pure and BHO-doped SmBCO film.

# 謝辞

本研究の一部は、科学研究費補助金(20686065, 19676005, 25289358)及び特別研究員奨励費(25002829)の助成を受けて実施したものである。

- [1] A. Tsuruta et al.: IEEE Trans. Appl. Supercond. 23 (2013) 8001104.

- [2] D. T. Verebelyi et al.: Appl. Phys. Lett. 76 (2000) 1755.

- [3] D. T. Verebelyi et al.: IEEE Trans. Appl. Supercond. 9 (1999) 2655.

# SmFeAs(O,F), Ba(Fe,Co)<sub>2</sub>As<sub>2</sub>, FeTe<sub>0.5</sub>Se<sub>0.5</sub>薄膜の CaF<sub>2</sub>基板界面近傍の微細構造 Microstructures of the vicinity of interface

between SmFeAs(O,F), Ba(Fe,Co)2As2, FeTe05Se05 thin films and CaF2 substrate

一瀬中,塚田一郎(電中研);鍋島 冬樹,今井良宗,前田京剛(東大);Kurth Fritz, Holzapfel Bernhard,飯田和昌(IFW-Dresden);上田真也,内藤方夫(東京農工大)

ICHINOSE Ataru, TSUKADA Ichiro (CRIEPI); NABESHIMA Fuyuki, IMAI Yoshinori, MAEDA Atsutaka (The Univ. of Tokyo); KURTH Fritz, HOLZAPFEL Bernhard, IIDA Kazumasa (IFW-Dresden); UEDA Shinya, NAITO Michio (TUAT) E-mail: ai@criepi.denken.or.jp

#### 1. はじめに

鉄系超電導材料は、AsあるいはSe(Te)の四面体の中心に Fe が配置され、この四面体構造が 2 次元につながった面が 超電導を担っていると考えられている。Lee らは、様々な鉄系 超電導体の  $T_c$ と As-Fe-As のボンド角との関係を調べ, その 関係がほぼ一つの曲線上に乗ることを見いだした(1)。また、Tc と結晶構造の関係に関する研究として、As の Fe 面からの高さ と T<sub>C</sub>の関係を議論したものもある<sup>(2)</sup>。このように, 鉄系超電導 材料は、格子の変形に伴い  $T_{\rm C}$  が変化する材料である。鉄系 超電導薄膜は, 基板材料により結晶格子の a 軸長, c 軸長が 変化する。SmFeAs(O,F)薄膜(1111 薄膜), BaFe2As2 薄膜 (122 薄膜), FeTe<sub>0.5</sub>Se<sub>0.5</sub> 薄膜(11 薄膜)において, 基板材料 を酸化物基板から CaF<sub>2</sub>基板にすることにより, 超電導薄薄膜 の結晶格子の a 軸長が縮み, c 軸長が伸びるという変形が生 じる。この結晶格子の変形とともに臨界温度が上昇するが (3-5) この変形の全てを単純に基板からのエピタキシャル歪で理解 することはできない(6)。そこで、透過型電子顕微鏡を用いて薄 膜と基板の界面近傍の微細構造解析を行い, 界面状態を明 らかにした。

# 2. 実験方法

1111 薄膜は Molecular Beam Epitaxy (MBE) 法を用いて、122 薄膜と 11 薄膜は Pulsed-Laser Deposition (PLD) 法により  $CaF_2(100)$ 基板上に作製した。得られた薄膜の電気抵抗率の温度依存性、および、臨界温度  $T_C$ を測定した。各膜の作製条件および  $T_C$ を Table I に示す。

集束イオンビーム装置を用いてマイクロサンプリング法により微小領域を切り出し、薄片化することにより微細構造観察試料を準備した。断面構造観察には透過型電子顕微鏡(JEM-ARM200F)を用い、明視野像から原子の配列状態を、暗視野像は ~コントラスト像として EDX の組成分析と合わせて組織の構成元素を調べた。

# 3. 結果および考察

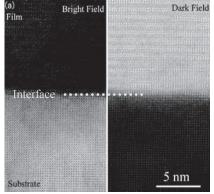

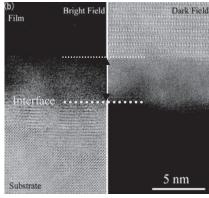

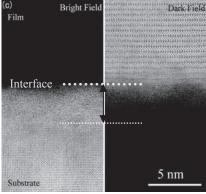

Fig. 1 に 3 つの超電導薄膜の High-Resolution Scanning TEM (HRSTEM) 像を示す。暗視野像とEDXの組成分析から 決定した基板と薄膜の界面を Fig. 1 に示す。 Fig. 1 より 1111 薄膜は反応層が無く、非常にきれいな界面を有していたが、 122 薄膜と 11 薄膜は反応層が存在していた。また、 122 薄膜の反応層は主に薄膜側に存在していたのに対し、 11 薄膜の反応層は基板側に存在していた。このように、同じ $CaF_2$  基板を用いても、3 つの薄膜で界面状態が全く異なっていることが分かった。 電子線回折から見積もった a 軸長と基板との関係より、 1111 薄膜ではエピタキシャル歪が有効に働いているが、他の 2 つの薄膜では有効に働いていないことが分かった。これは、界面に反応層が存在しているためと考えられる。

# 4. 謝辞

HRSTEM観察において、日本電子株式会社の安原氏、平井氏にご協力いただいた。本研究は科学技術振興機構の戦略的国際共同研究プログラム(SICORP)およびIRON-SEA(No. 283141)の助成を受けて実施したものである。

# 参考文献

- 1. C-H. Lee, et al., J. Phys. Soc. Jpn. 77 (2008) 083704

- 2. K. Kuroki, et al., Phys. Rev. B 79 (2009) 224511

- 3. S. Ueda, et al., Appl. Phys. Lett. 99 (2011) 232505

- 4. F. Kurth, et al., Appl. Phys. Lett. 10 (2013) 142601

- 5. Y. Imai, et al., Appl. Phys. Express 3 (2010) 043102

- A. Ichinose, et al., Supercond. Sci. Technol. 26 (2013) 075002

**Table I.** Film growth conditions and  $T_{\rm C}$ .

| Material               | SmFeAs(O,F)    | Ba(Fe,Co)As <sub>2</sub> | $FeTe_{0.5}Se_{0.5}$ |

|------------------------|----------------|--------------------------|----------------------|

| Technique              | MBE            | PLD                      | PLD                  |

| Substrate              | $CaF_{2}(001)$ | $CaF_{2}(001)$           | $CaF_{2}(001)$       |

| Temperature            | 650°C          | 700°C                    | 280°C                |

| Laser                  | -              | KrF, 7 Hz                | KrF, 10 Hz           |

| $T_{\rm C}^{\  \  90}$ | 56.5 K         | 26.9 K                   | 16.9 K               |

| $T_{\rm C}^{10}$       | 54.3 K         | 25.0 K                   | 16.0 K               |

The  $T_C^{90}$  and the  $T_C^{10}$  are defined as 90% and 10% of the normal-state resistivity, respectively, at 20 K for the FeTe<sub>0.5</sub>Se<sub>0.5</sub>, 30 K for the Ba(Fe,Co)<sub>2</sub>As<sub>2</sub>, and 60 K for the SmFeAs(O,F) thin films.

**Fig. 1.** Cross-sectional HRSTEM images of (a) SmFeAs(O,F), (b) Ba(Fe,Co)As<sub>2</sub>, and (c) FeTe<sub>0.5</sub>Se<sub>0.5</sub> thin films, respectively. The right image is a bright filed image and the left image is a dark field image as *z*-contrast.

# 単結晶粉末を用いた SmFeAsO<sub>1-x</sub>F<sub>x</sub>超伝導テープの開発

Fabrication of SmFeAsO<sub>1-x</sub>F<sub>x</sub> superconducting tape using powdered single crystals

藤岡 正弥 (NIMS), 岡崎 宏之 (NIMS), Saleem. J. Denholme (NIMS), 出村 郷志 (NIMS), 出口 啓太 (NIMS), 原 裕 (NIMS), 山木 琢磨 (NIMS), 山下 愛智 (NIMS) 山口 尚秀 (NIMS), 竹屋 浩幸 (NIMS), 熊倉 浩明 (NIMS), 高野 義彦 (NIMS)

FUJIOKA Masaya (NIMS), OKAZAKI Hiroyuki (NIMS), Saleem. J. Denholme(NIMS), DEMURA Satoshi (NIMS)

DEGUCHI Keita(NIMS), HARA Hiroshi (NIMS), YAMAKI Takuma (NIMS), YAMASHITA Aichi (NIMS),

YAMAGUCHI Naohide(NIMS), TAKEYA Hiroyuki(NIMS), KUMAKURA Hiroaki(NIMS), TAKANO Yoshihiko(NIMS)

FUJIOKA.Masaya@nims.go.jp

#### 1. はじめに

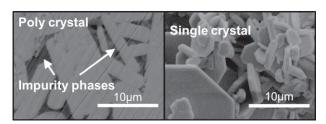

超伝導線材における実用化には 105 A/cm2 の臨界電流密 度が一般に必要とされる。現在、1111 鉄系超伝導線材にお いても 2.2×10<sup>4</sup> A/cm<sup>2</sup> に至るまで研究が進んでいる。近年、 1111 鉄系超伝導線材はEx-situ PIT法を用いて作製される事 が主流であり、この方法では一旦鉄系超伝導体を合成し、そ の粉末を超伝導線材のコアとして用いる。しかし、1111 鉄系 超伝導体を固相反応で作製する場合、アモルファスの不純物 相が結晶グレインの周囲に形成される。これは現在この系の 超伝導特性を阻害するもっとも大きな問題の一つである。 我々のグループではフラックス法を用いて、十分にフッ素濃 度が高い Sm-1111(SmFeAsO<sub>1-x</sub>F<sub>x</sub>)単結晶粉末の成長に成功 した。Fig. 1 で示すように、単結晶粉末は多結晶体で見られ るようなアモルファスの不純物相を一切形成しないので、多結 晶粉末を用いたEx-situ PIT 法で問題となっている結晶グレイ ン間の弱結合を改善する可能性がある。また、Ex-situ PIT 法 の最終過程である再焼結では、結晶内のフッ素濃度が減少し て、超伝導特性を著しく低下させる事が知られている。そのた め、再焼結時にフッ素濃度を補うための添加物を加える必要 がある。本研究では単結晶粉末を用いて超伝導テープを作 製するにあたり、まずは単結晶粉末の超伝導特性を明らかに し、その後必要となる添加物を選定し、Ex-situ PIT 法への適 用を試みる。

Fig.1 SEM images of the polished surface of poly crystal SmFeAsO<sub>1-v</sub>F<sub>v</sub>, and single crystal SmFeAsO<sub>1-v</sub>F<sub>v</sub>.

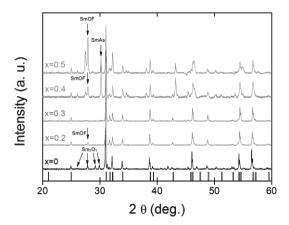

Fig.2 XRD pattern for  $SmFeAsO_{1-x}F_x$ . (x = 0, 0.2, 0.3, 0.4, 0.5)

# 2. 実験方法

本研究では超伝導コアに単結晶の $SmFeAsO_{1-x}F_x$ の粉末を用いる。単結晶粉末はCsClを使ったフラックス法により合成し、CsClは流水で洗い流す。単結晶試料のフッ素濃度は仕込み量でx=0.20,0.30,0.40,0.50と変化させて、実際のフッ素のフッ素濃度は格子定数の変化から見積もる。また、得られた単結晶の超伝導特性は磁化測定、電気抵抗測定から調べる。電気抵抗測定に関しては、1つの単結晶粉末に対してFIBを使用し、磁場中における超伝導特性に関しても測定を行う。さらに、再焼結後の良質な超伝導コアの形成をめざし、フッ素を含む添加物を加え、熱処理し、超伝導特性の変化を調べる。

#### 3. 結果

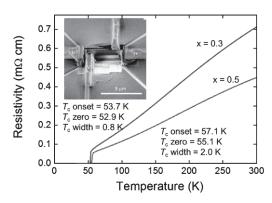

Fig. 2 に得られた XRD の結果を示す。x=0.3 以上では SmOF の不純物が増加しており、それ以下のフッ素濃度でも 不純物が形成されている。一方、x=0.3 ではほぼ単相の SmFeAsO<sub>1-x</sub>F<sub>x</sub> が得られており、格子定数から見積もられたフッ素濃度は x=0.15 程度であった。FIB を用いた電気抵抗測定では Fig.3 に示されるように、仕込み量で x=0.3 の時、超 伝導転移温度が 53. 7K であり、仕込み量で x=0.5 の試料では 57.1Kを観測した。

Fig. 3 Resistivity versus temperature for the samples from x = 0.3, 0.5. Insert shows the device after FIB process.

#### 4. まとめ

本研究ではフラックス法から得られる単結晶粉末を用いて、超伝導テープを作製する。単結晶粉末の長所としてはアモルファスの不純物が一切含まれない事である。また、この試料は圧延に対して c 軸配向性が高く、テープ線材に適している。本研究ではフッ素の仕込み量が x=0.3 の時、ほとんど不純物が形成されず転移温度も 53.7 Kと比較的高い試料の合成に成功した。さらに、x=0.5 の試料では転移温度が57.1 Kを示し、現在得られている単結晶では鉄系最大の超伝導転移温度を示した。会議では、超伝導テープ化にむけて、より詳細な結果を報告する。